Problem 1 : Zero

这题同样要求构建一个电路,没有输入端口,只有一个输出端口,但这次输出端口时钟驱动逻辑 0 。

如果你完成了前一道题,那么这题也自然不在话下,尝试一下不借助提示来解决这个问题。

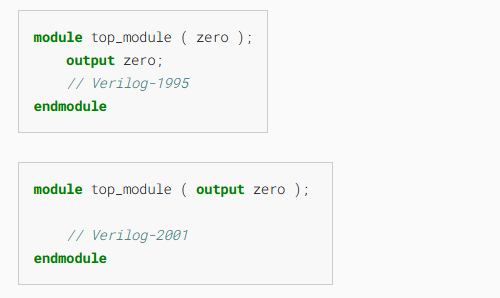

注意:HDLBits 使用 Verilog-2001 标准语法来声明端口,因为相比老标准 Verilog-1995 的端口定义方式,新标准更加清晰,并方便修改端口。但如果你想的话,也可以将端口声明改为 1995 标准(应该不想吧)。举例而言:下方两种端口声明方式都是可接受并等价的。

部分题目提供了 Hint,可以给你提供一些帮助。比如这题的提示:

如果你什么也不做,在 Quartus 中,输出端口会被默认赋值为 0,所以这题超简单,直接提交即可。

当然,使用默认值是危险的,相当不推荐的编码风格。

解答与分析

module top_module

(

output zero

);

// Module body starts after semicolon

assign zero = 1'b0;

endmodule