Problem 0 : Step one

欢迎来到 HDLBits!

数字逻辑电路学习的挂挡起步往往是艰难的,因为你一开始就发现有一堆东西等着你去学习:新的概念,一种新的硬件描述语言(Hardware Description Language,比如 Verilog),几种软件工具(ISE,Vivado,Modelsim,Quartus等等),以及可能包括一块 FPGA 开发板,所有一切都同时等着你去学习,学习曲线略微陡峭。好在 HDLBits 提供了在线练习数字电路设计与调试的功能,只需要通过执行页面上的 Simulate 按钮,就能为你的学习助力。

设计一个数字电路需要以下几步:编写 HDL 硬件描述语言,比如使用 Verilog;编译(综合)代码为一个数字电路;仿真分析电路的功能和时序;最后修正错误,Kill those bugs。

编写代码

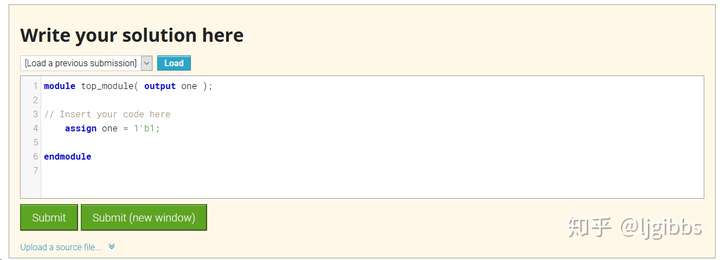

最简单的方式是直接在 HDLBits 网页下方的代码框内编写你的代码,因为网页已经帮你生成了部分代码,比如模块的输入输出端口,你只需要补全剩余的代码。

你也可以在其他的编辑器上完成代码的编写,然后使用上传功能,上传你的 v 文件,这样会有些繁琐,但你可以利用到编辑器的语法补全,代码片段等特性。

之后点击页面上的 Simulate 按钮,对代码进行编译(综合),仿真。

编译(逻辑综合)

你的代码会通过 Altera Quartus 的综合器综合为硬件电路。Quartus 会生成一组综合信息,通过 Show Quartus messages 可以显示/隐藏他们。通过这些信息可以进行相应的修改,减少代码中的警告,但一般没有必要清除所有的警告,有些警告就随它去吧。

仿真

综合后的电路会通过仿真来检查其功能是否正确。HDLBits 使用 ModelSim 同时仿真你的电路和参考电路,然后比较两者的输出。仿真报告关注两个方面:

一是,会报告你的电路的输出与参考电路的输出是否完全一致,(不存在 mismatch)。或者当两者输出不一致时,mismatch 的数量。mismatch 代表某一时刻两者的输出并不一致,正确的电路中不存在 mismatch。

第二,仿真报告会产生你的电路运行测试向量时,输出的信号波形,波形分为三组:输入信号,待测试电路的输出信号,参考电路的输出信号。

注意:不要修改题目中给定的模块以及端口的名称,否则会造成仿真错误。

结果状态

如果你的电路完全正确,那么你会看到 Status: Success! 当然情况也有不妙的时候:

- Compile Error — 电路综合失败

- Simulation Error — 电路综合成功,但是仿真存在错误

- Incorrect — 电路综合,仿真成功,但输出结果和参考结果不同。

你可以通过 My Stats 页面查询自己在所有题目中的状态,以及完成度在所有参与用户中的排名,通过注册账号,可以在多个浏览器上进行访问。

牛刀小试

说了这么多,终于到这道题的练习环节,第一题将帮助你熟悉 HDLBits 所使用的综合与仿真接口,每道题目都会给出所需电路的描述。

构建一个电路,没有输入端口,只有一个输出端口,输出端口时钟驱动逻辑 1 ,即逻辑高。

模块的端口已经给出,一般来说,这个电路通过一行代码就可以构建。

解答与分析

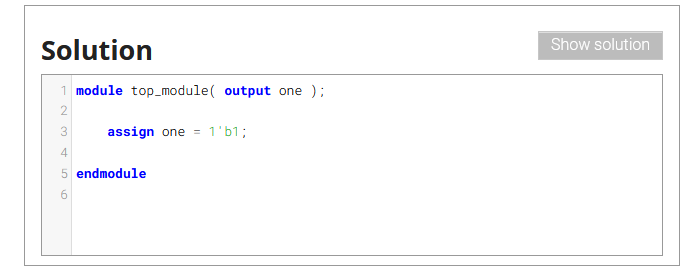

这个题目很简单,assign one = 1'b1; 即可。

1 在数字逻辑中代表 logic high,而 0 代表 logic low。

通过这题可以了解 HDLBits 的基本操作以及数字逻辑的一些简单概念,在完成正确的提交后,可以通过题目下方 Show Solution 查看到解答。目前看下来大部分的题目是有解答的,但你只有正确提交之后才能查看解答。

作者: ljgibbslf@zhihu

邮箱:lf_gibbs@163.com